You are receiving this because you are subscribed to this thread. "the language has many other problems so this one isn't worth checking".

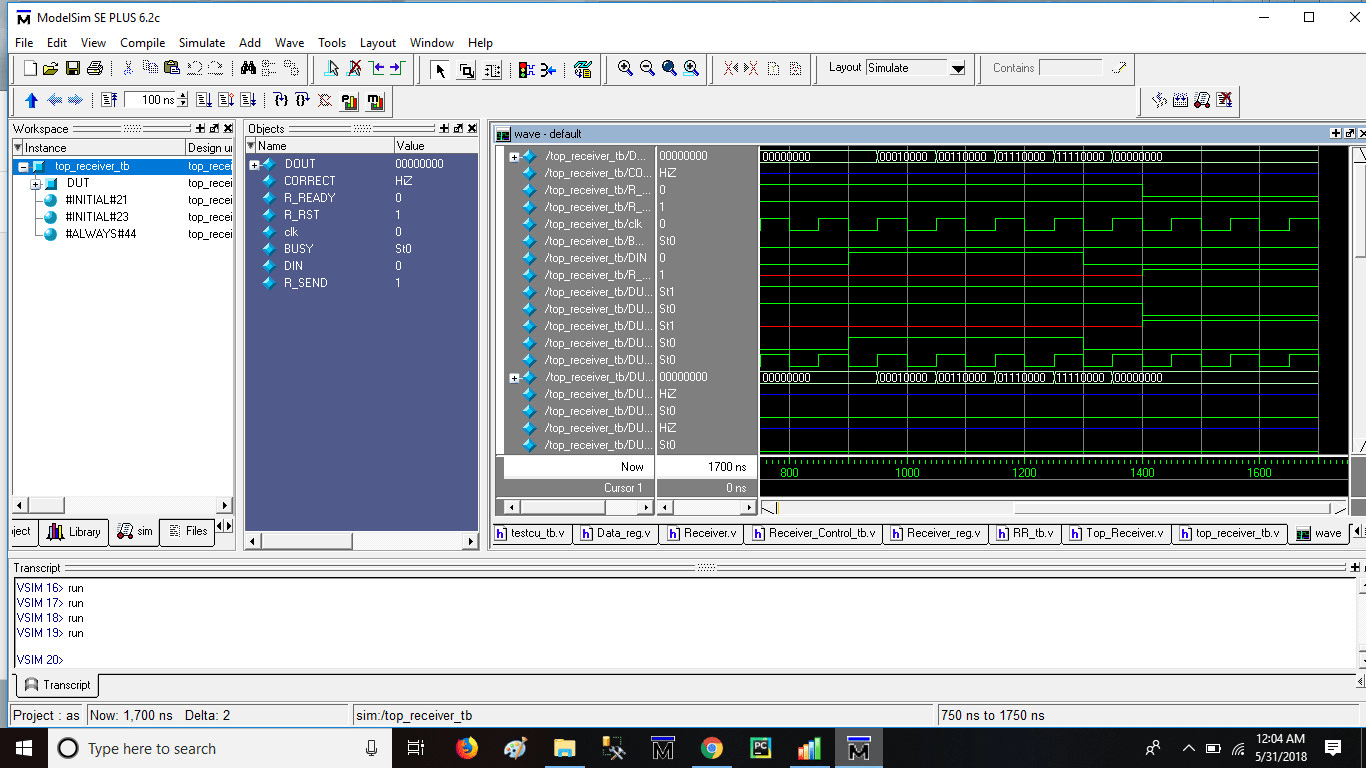

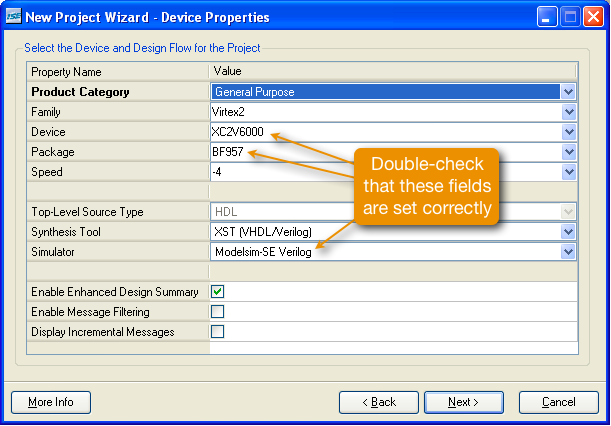

#Modelsim verilog simulator#

A.4 Linking PLI applications to the Model Technology ModelSim simulator The. I can understand the reasoning of "we don't need *this* safety feature",Īssumingly because the potential issues are restricted to a small space,īut I can't get behind the reasoning of "this is how everyone does it" or A User's Guide and Comprehensive Reference on the Verilog Programming. In order to prevent bugs caused by implicit wires. default_nettype none is a safety feature exercised Why is Verilog any different? There are tons of ways to shoot yourself in

#Modelsim verilog code#

Specification but has a high propensity to be incorrect. We present a system Verilog/C code creation and compilation system that creates a ModelSim-Matlab shared memory interface optimized for the input/output. Sanitizers to try to detect code which is allowed by the language It is well known that languages like C++ allow you to shoot yourself in theįoot, and as a result there has been a ton of work on linters and Something that's "accepted" from the language but yet it causes 70% of I don't necessarily disagree with the change as much as I disagree withĬ++ code is littered with off by 1 errors and unsafe memory accesses. On Fri, at 1:39 PM Austin Rovinski wrote: Implicit wires are used everywhere in verilog by everyone

I can understand the reasoning of "we don't need this safety feature", assumingly because the potential issues are restricted to a small space, but I can't get behind the reasoning of "this is how everyone does it" or "the language has many other problems so this one isn't worth checking". Why would we not exercise a safety feature if it exists? default_nettype none is a safety feature exercised in order to prevent bugs caused by implicit wires. Why is Verilog any different? There are tons of ways to shoot yourself in the foot with Verilog. It is well known that languages like C++ allow you to shoot yourself in the foot, and as a result there has been a ton of work on linters and sanitizers to try to detect code which is allowed by the language specification but has a high propensity to be incorrect. It's something that's "accepted" from the language but yet it causes 70% of security vulnerabilities. I don't necessarily disagree with the change as much as I disagree with the reasoning.Ĭ++ code is littered with off by 1 errors and unsafe memory accesses.

0 kommentar(er)

0 kommentar(er)